Use LTspice to Model Decap and Bondwire Inductance: Accurate modeling of decoupling capacitor inductance and bondwire inductance is vital for high-speed and power electronics design. LTspice makes it possible to simulate these effects realistically—helping engineers predict noise, voltage spikes, and circuit performance under real-world conditions. In this article, we’ll explore how to set up these models effectively in LTspice, understand their impact, and use them to refine your designs.

1. Why Model ESL in Decoupling Capacitors?

Equivalent Series Inductance (ESL) in decoupling capacitors represents the inductance due to internal construction, leads, and packaging. Ignoring ESL leads to misleading results—real circuits often display high-frequency voltage spikes and resonances not seen in ideal models.

On forums, designers experience unexplained ESL spikes when they include real-world series inductance in simulations, particularly in switching regulator output caps. One user reported ~1.5 V peak-to-peak spikes around mid-transient, compared to smooth behavior with ideal caps. This highlights how vital it is to include ESL when simulating power integrity in LTspice.

2. Incorporating ESL in LTspice Capacitor Models

LTspice allows you to specify series inductance (Ls) directly within a capacitor’s properties. To enable it:

- Insert a capacitor symbol.

- Double-click and fill in the Series Inductance field with the measured or specified value.

- Optionally also specify series resistance (ESR).

When enabled, LTspice simulates more realistic behavior, including high-frequency resonances and transient spikes

For enhanced accuracy, many manufacturers (like Wurth) offer SPICE models with built-in ESL, ESR, and parasitic capacitance—preferable for matching real device behavior

3. Modeling Bondwire Inductance in LTspice

Bondwire inductance refers to the tiny inductance from the thin metal wires connecting an IC die to its package pins. These parasitics matter in high-speed and power circuits, causing overshoot, ringing, and EMI if neglected.

Modeling Options:

Use discrete inductors: Insert an inductor (named Lbond) in series with power or signal leads. Estimate bondwire inductance as approximately 1 nH/mm—adjust to match package specifics.

Behavioral models: LTspice allows defining inductances that depend on current or other variables, using behavioral sources and expressions—though complex

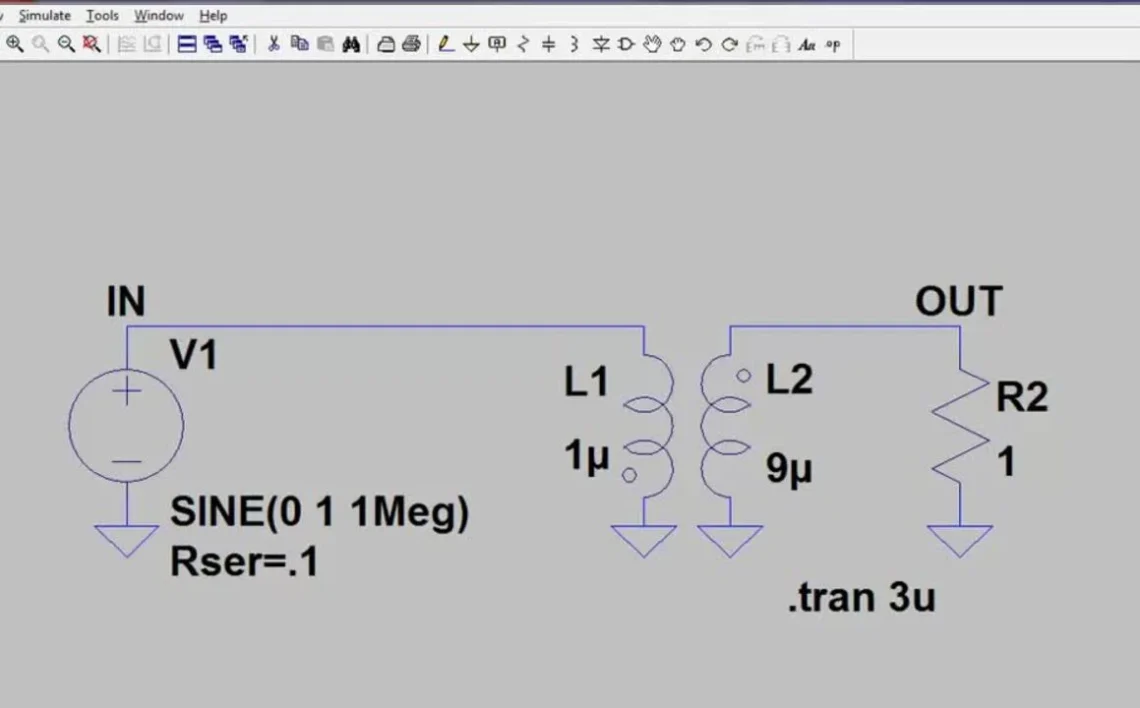

Transformers or mutual coupling: For advanced modeling involving shared magnetic paths (e.g., multi-wire bonding), use coupled inductors with the K directive to capture mutual inductance

4. Combining ESL and Bondwire Models: Simulation Workflow

Here’s a step-by-step approach to simulate a realistic power path:

- Place the decoupling capacitor and enter ESL and ESR.

- Add series inductors representing bondwire and trace inductance.

- Inject transient loads, such as step current pulses or switching regulator pulses.

- Run transient (

.tran) and frequency (.ac) simulations, then observe voltage at power pins, overshoot, and ringing.

Tip: When capacitive ESL causes unexpected spikes, refer to the forum case where including real ESL produced much larger transient artifacts than idealized models. This reflects true circuit sensitivities.

5. Advanced Techniques: Saturation and Core Effects

For inductors that saturate (e.g. inductive traces or power inductors), LTspice offers advanced non-linear models like the Chan model with hysteresis and saturation characteristics

While bondwires don’t saturate, modeling saturation provides insight into real inductors. Similarly, mutual inductance between parallel current paths within packages can be approximated with coupled inductors, although precise modeling requires specialized data.

6. Best Practices for Realistic Power Integrity Simulation

To maximize accuracy in LTspice simulations:

-

Use manufacturer-provided SPICE models when available.

-

Characterize ESL and bondwire inductance—via datasheets, PCB calculators, or measured prototypes.

-

Use

.stepanalysis to assess sensitivity across ESL and inductance values. -

Inspect waveforms carefully, especially during fast transients.

-

Cross-reference with physical testing, since simulations can highlight but must be confirmed against reality.

By combining real component models, bondwire approximations, and transient stress tests, you achieve a simulation environment that mirrors physical circuit behavior.

Conclusion

Mastering decoupling capacitor modeling and bondwire inductance in LTspice puts you ahead in reliable, high-performance power electronics design. By incorporating ESL, ESR, and parasitics, you move beyond simplistic models and start capturing the true dynamic behavior of real hardware.

Remember: even small inductances can cause significant voltage anomalies in fast circuits. Use LTspice’s capabilities—alongside real-world data—to simulate, iterate, and optimize your designs before committing them to silicon or PCB.